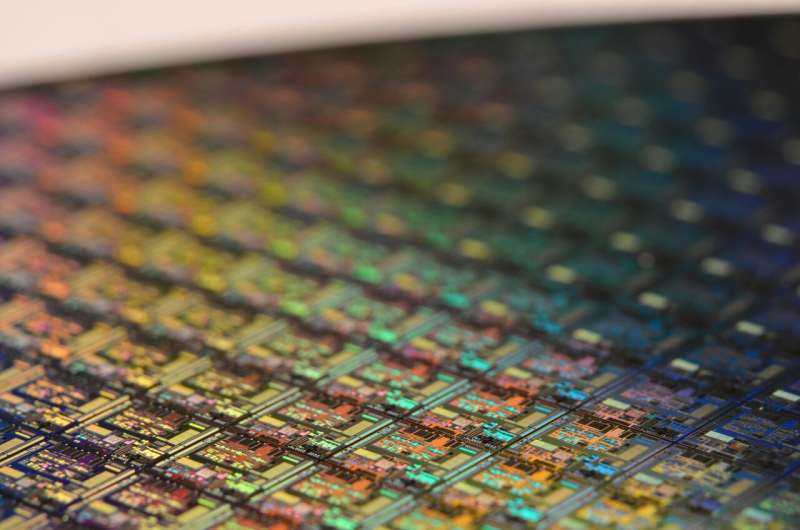

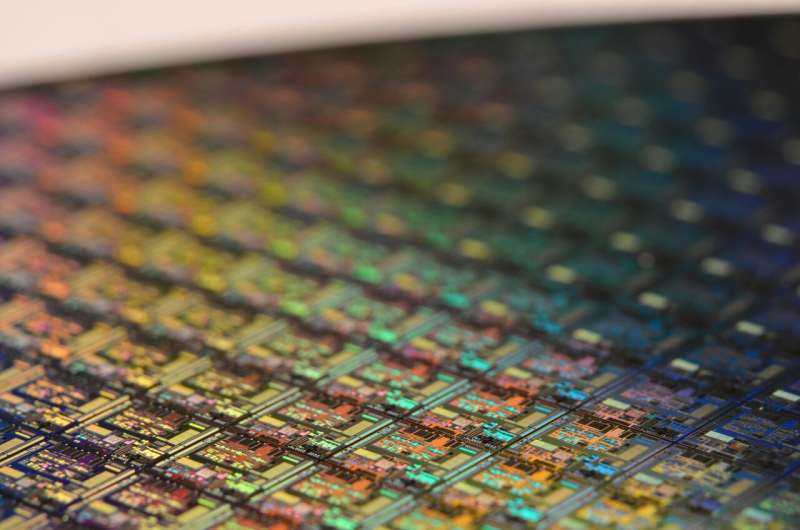

The phrase “advanced chip packaging” might conjure images of a fancy Pringles can. For those who manufacture semiconductors—also known as integrated circuits, chips or microchips—it represents a new frontier, a race to design and mass produce the next generation of semiconductors that use less energy while delivering more computing power.

Traditionally completed near the end of the manufacturing process, chip packaging is the arranging and installation of a chip with its electrical and protective components on a “substrate,” or base plate, made of silicon or other materials.

Penn State plays a leading role in America’s push for advancement in chips packaging as the home of the Center for Heterogeneous Integration of Micro Electronic Systems (CHIMES), a partnership of 15 universities to initiate advances in chip integration and packaging.

Additionally, several Penn State researchers are focused on the topic, including Madhavan Swaminathan, department head of electrical engineering, William E. Leonhard Endowed Chair in the School of Electrical Engineering and Computer Science and director of CHIMES; and Daniel Lopez, Liang Professor of Electrical Engineering, director of the Penn State Nanofabrication Lab and the founder of the Mid-Atlantic Semiconductors Hub.

In a Q&A with Penn State News, Swaminathan and Lopez, both affiliated with the Penn State Materials Research Institute, discussed the future of chip manufacturing and advanced packaging and how Penn State-led initiatives like CHIMES and MASH help turn innovations in the lab into reliable domestic production.

A guiding principle in chip manufacturing is Moore’s Law, which predicted that the number of transistors that can be packed in an integrated circuit would double every 18 months, resulting in smaller but more powerful semiconductors. Is this still achievable over the next decade?

Swaminathan: The main driver behind Moore’s law is economics. The cost of a transistor used to be seven bucks in the early 1960s. Today, the cost of the transistor is one nano dollar—one-billionth of a dollar. The only item you can probably purchase for a nano dollar is a transistor. This has been the result of Moore’s law.

The shrinkage of the transistor over the years has allowed more transistors to be integrated on a single chip and has enabled the increase in performance of systems they enable. However, recently we have reached an inflection point where the cost of the transistor is beginning to rise due to the cost of the equipment and processes used to shrink the transistor any further, and that is where packaging comes in. Advanced packaging is a means to continue Moore’s law, where systems of the future can continue to be economical while the performance continues to increase.

How will advanced packaging techniques help in this regard?

Swaminathan: There are five important metrics that drive system development: power, performance, size, cost and reliability. Future systems need to consume less power, which translates into energy savings for our planet. The computational speeds of systems need to continuously increase to enable the solution to difficult problems in a reasonable time, also referred to as performance. The size of systems needs to be reduced, especially when mobility becomes important. And, of course, these systems need to be affordable and highly reliable as well. The role of advanced packaging becomes critical when all these metrics are considered simultaneously to optimize the system attributes.

Let’s apply that to something commonplace, like a cell phone. Could you describe a typical chip architecture and how advanced packaging techniques could be applied in the manufacturing process?

Swaminathan: Ask yourself “what does a smart phone do today?” It allows you to communicate, compute and sense. All these functions are enabled through the creation, manipulation and processing of data. It turns out that the types of transistors required to support the three functions are not the same. In fact, the transistor technologies required are so disparate that these transistors cannot be combined on a single chip. In addition, supporting each of these functions may require separate chips as well—for example, memory chips that enable the storage of data different from the processor chips.

These chips need to be connected to each other, along with other non-transistor components, to build the smart phone. Since smart phones are cost-sensitive and size is an important attribute, these need to be considered as well. All this is enabled through advanced packaging that allows signals to be transmitted back and forth between chips while the chips consume minimal power. As the chips generate heat, packaging efficiently removes the heat while protecting the transistors from environmental conditions such as vibration, shock, temperature, humidity and other factors.

Lopez: In addition to the electronic components, a modern smart phone could have as many as 30 micro-mechanical sensors. These sensing elements, known as micro-electromechanical systems (MEMS), are vibrating structures smaller than the diameter of a human hair. They are used to measure time, speed, location and orientation of the phone, and they are critical components in the cell phone’s microphones and cameras. Since MEMS-based sensors must interact with the environment, packaging them requires special structures, materials and processes that are not always compatible with the packages used for transistors.

Today’s smart cell phone architectures are spectacular examples of the integration of multiple technologies in a device, but much more research is still needed to optimize the integration processes and the performance of multi-component systems.

CHIMES helps take advanced packaging a step further in the manufacturing process through heterogenous integration. What is that and how does it build on advanced packaging techniques?

Swaminathan: Heterogeneous Integration refers to connecting chips from different process technologies on a package to maximize the power, performance, size, cost and reliability of the overall system. Since these chips can originate at different fabrication facilities, the time to design and bring them to market can be reduced.

Such an approach requires the development of new system concepts, transistor devices, various electronic and photonic components such as antennas, capacitors, inductors, waveguides, new materials for the efficient transmission of signals and heat removal, chips communicating with each other side by side and on top of each other, and many more. This is the focus of CHIMES, where our metrics are driven based on emerging applications and a 10-year outlook.

Last fall, the $3 billion National Advanced Packaging Manufacturing Program (NAPMP) was announced to drive U.S. leadership in advanced packaging and stimulate a domestic semiconductor manufacturing presence. This spring, MASH held a workshop focused on the topic with the program’s director, Subu Iyer, as the keynote speaker. What was the key takeaway from that workshop?

Swaminathan: NAPMP has two major goals: to establish American leadership by onshoring advanced packaging here in the United States, supported by a resilient supply chain, and to enable education and workforce development in advanced packaging. The key technological drivers to achieve the former is scale-in—reducing the dimensions of the wires in the package such that they are comparable to wiring on-chip—and scale-out—increasing the size of packages so that they become comparable in size to printed circuit boards. The combination of the two will help blur the interface between what is on-chip and off-chip, a need that heterogeneous integration helps address.

Lopez: With respect to the latter, education and workforce development goals need to be broad, and that includes reaching K-12 students, those in two-year colleges, veterans, people with disabilities, and those in four-year and advanced degree programs. The MASH workshop provided a unique forum to discuss these topics and resulted in multiple working groups that are currently developing solutions to many of the problems described above. The working groups include experts from academia, industry and government.

In 2021, the federal government passed the CHIPS Act (Creating Helpful Incentives to Produce Semiconductors for America) aimed at boosting semiconductor manufacturing in the United States. How are MASH and CHIMES helping to translate the knowledge generated by Penn State and partner institutions into a thriving chip manufacturing ecosystem in the Mid-Atlantic region?

Swaminathan: Universities are excellent in pre-competitive research, with some excelling in applied research as well. Industry, on the other hand, operates in a competitive world, especially in manufacturing. There is a big disconnect between the two sides, where innovations in the university laboratories are often lost and do not make it into manufacturing. This gap is often referred to as the “valley of death.” This is exactly what we hope to correct through CHIMES and MASH, by introducing translational work through prototyping and piloting.

Prototyping enables higher levels of integration at the University while piloting in an industry setting provides for achieving statistical significance prior to manufacturing. The handshake between the two can result in the “valley of death” becoming a “valley of opportunity.”

Lopez: The academic and industrial organizations partnering with CHIMES and MASH provide access to a unique chip manufacturing ecosystem in the Mid-Atlantic region that we hope will revolutionize the future of electronics in the U.S. MASH and CHIMES are working together to design novel curriculum activities that expand opportunities for training for underrepresented minorities in STEM academic careers.

Pennsylvania State University

Q&A: How advanced chip packaging can help redesign the future of semiconductors (2024, May 8)

retrieved 8 May 2024

from https://techxplore.com/news/2024-05-qa-advanced-chip-packaging-redesign.html

part may be reproduced without the written permission. The content is provided for information purposes only.

The phrase “advanced chip packaging” might conjure images of a fancy Pringles can. For those who manufacture semiconductors—also known as integrated circuits, chips or microchips—it represents a new frontier, a race to design and mass produce the next generation of semiconductors that use less energy while delivering more computing power.

Traditionally completed near the end of the manufacturing process, chip packaging is the arranging and installation of a chip with its electrical and protective components on a “substrate,” or base plate, made of silicon or other materials.

Penn State plays a leading role in America’s push for advancement in chips packaging as the home of the Center for Heterogeneous Integration of Micro Electronic Systems (CHIMES), a partnership of 15 universities to initiate advances in chip integration and packaging.

Additionally, several Penn State researchers are focused on the topic, including Madhavan Swaminathan, department head of electrical engineering, William E. Leonhard Endowed Chair in the School of Electrical Engineering and Computer Science and director of CHIMES; and Daniel Lopez, Liang Professor of Electrical Engineering, director of the Penn State Nanofabrication Lab and the founder of the Mid-Atlantic Semiconductors Hub.

In a Q&A with Penn State News, Swaminathan and Lopez, both affiliated with the Penn State Materials Research Institute, discussed the future of chip manufacturing and advanced packaging and how Penn State-led initiatives like CHIMES and MASH help turn innovations in the lab into reliable domestic production.

A guiding principle in chip manufacturing is Moore’s Law, which predicted that the number of transistors that can be packed in an integrated circuit would double every 18 months, resulting in smaller but more powerful semiconductors. Is this still achievable over the next decade?

Swaminathan: The main driver behind Moore’s law is economics. The cost of a transistor used to be seven bucks in the early 1960s. Today, the cost of the transistor is one nano dollar—one-billionth of a dollar. The only item you can probably purchase for a nano dollar is a transistor. This has been the result of Moore’s law.

The shrinkage of the transistor over the years has allowed more transistors to be integrated on a single chip and has enabled the increase in performance of systems they enable. However, recently we have reached an inflection point where the cost of the transistor is beginning to rise due to the cost of the equipment and processes used to shrink the transistor any further, and that is where packaging comes in. Advanced packaging is a means to continue Moore’s law, where systems of the future can continue to be economical while the performance continues to increase.

How will advanced packaging techniques help in this regard?

Swaminathan: There are five important metrics that drive system development: power, performance, size, cost and reliability. Future systems need to consume less power, which translates into energy savings for our planet. The computational speeds of systems need to continuously increase to enable the solution to difficult problems in a reasonable time, also referred to as performance. The size of systems needs to be reduced, especially when mobility becomes important. And, of course, these systems need to be affordable and highly reliable as well. The role of advanced packaging becomes critical when all these metrics are considered simultaneously to optimize the system attributes.

Let’s apply that to something commonplace, like a cell phone. Could you describe a typical chip architecture and how advanced packaging techniques could be applied in the manufacturing process?

Swaminathan: Ask yourself “what does a smart phone do today?” It allows you to communicate, compute and sense. All these functions are enabled through the creation, manipulation and processing of data. It turns out that the types of transistors required to support the three functions are not the same. In fact, the transistor technologies required are so disparate that these transistors cannot be combined on a single chip. In addition, supporting each of these functions may require separate chips as well—for example, memory chips that enable the storage of data different from the processor chips.

These chips need to be connected to each other, along with other non-transistor components, to build the smart phone. Since smart phones are cost-sensitive and size is an important attribute, these need to be considered as well. All this is enabled through advanced packaging that allows signals to be transmitted back and forth between chips while the chips consume minimal power. As the chips generate heat, packaging efficiently removes the heat while protecting the transistors from environmental conditions such as vibration, shock, temperature, humidity and other factors.

Lopez: In addition to the electronic components, a modern smart phone could have as many as 30 micro-mechanical sensors. These sensing elements, known as micro-electromechanical systems (MEMS), are vibrating structures smaller than the diameter of a human hair. They are used to measure time, speed, location and orientation of the phone, and they are critical components in the cell phone’s microphones and cameras. Since MEMS-based sensors must interact with the environment, packaging them requires special structures, materials and processes that are not always compatible with the packages used for transistors.

Today’s smart cell phone architectures are spectacular examples of the integration of multiple technologies in a device, but much more research is still needed to optimize the integration processes and the performance of multi-component systems.

CHIMES helps take advanced packaging a step further in the manufacturing process through heterogenous integration. What is that and how does it build on advanced packaging techniques?

Swaminathan: Heterogeneous Integration refers to connecting chips from different process technologies on a package to maximize the power, performance, size, cost and reliability of the overall system. Since these chips can originate at different fabrication facilities, the time to design and bring them to market can be reduced.

Such an approach requires the development of new system concepts, transistor devices, various electronic and photonic components such as antennas, capacitors, inductors, waveguides, new materials for the efficient transmission of signals and heat removal, chips communicating with each other side by side and on top of each other, and many more. This is the focus of CHIMES, where our metrics are driven based on emerging applications and a 10-year outlook.

Last fall, the $3 billion National Advanced Packaging Manufacturing Program (NAPMP) was announced to drive U.S. leadership in advanced packaging and stimulate a domestic semiconductor manufacturing presence. This spring, MASH held a workshop focused on the topic with the program’s director, Subu Iyer, as the keynote speaker. What was the key takeaway from that workshop?

Swaminathan: NAPMP has two major goals: to establish American leadership by onshoring advanced packaging here in the United States, supported by a resilient supply chain, and to enable education and workforce development in advanced packaging. The key technological drivers to achieve the former is scale-in—reducing the dimensions of the wires in the package such that they are comparable to wiring on-chip—and scale-out—increasing the size of packages so that they become comparable in size to printed circuit boards. The combination of the two will help blur the interface between what is on-chip and off-chip, a need that heterogeneous integration helps address.

Lopez: With respect to the latter, education and workforce development goals need to be broad, and that includes reaching K-12 students, those in two-year colleges, veterans, people with disabilities, and those in four-year and advanced degree programs. The MASH workshop provided a unique forum to discuss these topics and resulted in multiple working groups that are currently developing solutions to many of the problems described above. The working groups include experts from academia, industry and government.

In 2021, the federal government passed the CHIPS Act (Creating Helpful Incentives to Produce Semiconductors for America) aimed at boosting semiconductor manufacturing in the United States. How are MASH and CHIMES helping to translate the knowledge generated by Penn State and partner institutions into a thriving chip manufacturing ecosystem in the Mid-Atlantic region?

Swaminathan: Universities are excellent in pre-competitive research, with some excelling in applied research as well. Industry, on the other hand, operates in a competitive world, especially in manufacturing. There is a big disconnect between the two sides, where innovations in the university laboratories are often lost and do not make it into manufacturing. This gap is often referred to as the “valley of death.” This is exactly what we hope to correct through CHIMES and MASH, by introducing translational work through prototyping and piloting.

Prototyping enables higher levels of integration at the University while piloting in an industry setting provides for achieving statistical significance prior to manufacturing. The handshake between the two can result in the “valley of death” becoming a “valley of opportunity.”

Lopez: The academic and industrial organizations partnering with CHIMES and MASH provide access to a unique chip manufacturing ecosystem in the Mid-Atlantic region that we hope will revolutionize the future of electronics in the U.S. MASH and CHIMES are working together to design novel curriculum activities that expand opportunities for training for underrepresented minorities in STEM academic careers.

Pennsylvania State University

Q&A: How advanced chip packaging can help redesign the future of semiconductors (2024, May 8)

retrieved 8 May 2024

from https://techxplore.com/news/2024-05-qa-advanced-chip-packaging-redesign.html

part may be reproduced without the written permission. The content is provided for information purposes only.